Електронні мікросхеми Підтримка BOM Service TPS54560BDDAR абсолютно нові мікросхеми електронні компоненти

Атрибути продукту

| ТИП | ОПИС |

| Категорія | Інтегральні схеми (ІС) Регулятори напруги - DC Імпульсні регулятори постійного струму |

| Виробник | Texas Instruments |

| Серія | Eco-Mode™ |

| Пакет | Стрічка та котушка (TR) Відрізана стрічка (CT) Digi-Reel® |

| SPQ | 2500T&R |

| Статус продукту | Активний |

| функція | Крок вниз |

| Конфігурація виводу | Позитивний |

| Топологія | Бак, Split Rail |

| Тип виводу | Регульована |

| Кількість виходів | 1 |

| Вхідна напруга (хв.) | 4,5 В |

| Вхідна напруга (макс.) | 60В |

| Вихідна напруга (мін./фікс.) | 0,8 В |

| Вихідна напруга (макс.) | 58,8 В |

| Струм - вихід | 5A |

| Частота - Перемикання | 500 кГц |

| Синхронний випрямляч | No |

| Робоча температура | -40°C ~ 150°C (ТДж) |

| Тип монтажу | Поверхневий монтаж |

| Пакет / футляр | 8-PowerSOIC (ширина 0,154", 3,90 мм) |

| Пакет пристроїв постачальника | 8-SO PowerPad |

| Базовий номер продукту | TPS54560 |

1.Найменування IC, загальні знання пакетів і правила іменування:

Температурний діапазон.

C=0°C до 60°C (комерційний сорт);I=-20°C до 85°C (промисловий клас);E=-40°C до 85°C (розширений промисловий клас);A=-40°C до 82°C (аерокосмічний клас);M=-55°C до 125°C (військовий клас)

Тип упаковки.

A-SSOP;B-CERQUAD;C-TO-200, TQFP;D-керамічна мідна верхня частина;E-QSOP;F-Ceramic SOP;H- SBGAJ-Ceramic DIP;К-ТО-3;L-LCC, M-MQFP;N-Narrow DIP;N-DIP;Q PLCC;R - вузький керамічний DIP (300mil);S - ТО-52, Т - ТО5, ТО-99, ТО-100;U - TSSOP, uMAX, SOT;W - Wide Small Form Factor (300 mil) W-Wide Small Form Factor (300 mil);X-SC-60 (3P, 5P, 6P);Y-вузький мідний верх;Z-TO-92, MQUAD;D-Die;/PR-армований пластик;/W-вафля.

Кількість штифтів:

а-8;б-10;с-12, 192;д-14;е-16;ф-22, 256;г-4;h-4;i -4;Н-4;І-28;J-2;К-5, 68;Л-40;М-6, 48;N 18;О-42;П-20;Q-2, 100;Р-3, 843;С-4, 80;Т-6, 160;У-60 -6 160;У-60;V-8 (круглий);W-10 (круглий);Х-36;Y-8 (круглий);Z-10 (круглий).(круглий).

Примітка. Перша літера суфікса класу інтерфейсу з чотирьох літер – E, що означає, що пристрій має антистатичну функцію.

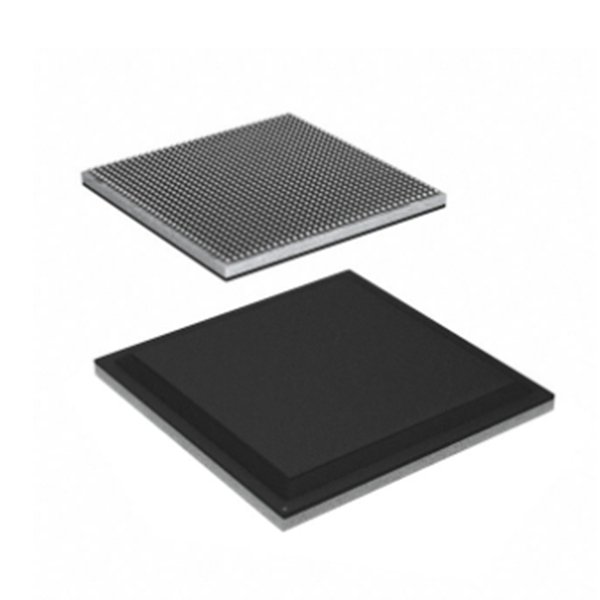

2.Розробка технології пакування

Найперші інтегральні схеми використовували керамічні плоскі корпуси, які продовжували використовуватися військовими протягом багатьох років через їх надійність і невеликий розмір.Комерційна упаковка схем незабаром перейшла на корпуси з подвійним рядком, починаючи з кераміки, а потім із пластику, а у 1980-х роках кількість контактів у схемах НВІС перевищила межі застосування пакетів DIP, що зрештою призвело до появи масивів контактних сіток і носіїв мікросхем.

Пакет для поверхневого монтажу з’явився на початку 1980-х років і став популярним наприкінці того ж десятиліття.Він має менший крок шпильок і має форму крила чайки або J-подібну форму.Наприклад, інтегральна схема малого розміру (SOIC) має на 30-50% меншу площу та на 70% меншу товщину, ніж еквівалентний DIP.Ця упаковка має штифти у формі крила чайки, що виступають з двох довгих сторін, і крок шпильок становить 0,05 дюйма.

Пакети малогабаритних інтегральних схем (SOIC) і PLCC.у 1990-х роках, хоча пакет PGA все ще часто використовувався для мікропроцесорів високого класу.PQFP і тонкий корпус малого контуру (TSOP) стали звичайним пакетом для пристроїв з великою кількістю контактів.Високоякісні мікропроцесори Intel і AMD перейшли з пакетів PGA (Pine Grid Array) на корпуси Land Grid Array (LGA).

Пакети Ball Grid Array почали з’являтися в 1970-х роках, а в 1990-х роках був розроблений пакет FCBGA з більшою кількістю контактів, ніж інші пакети.У корпусі FCBGA матриця повертається вгору та вниз і з’єднується з кульками припою на корпусі базовим шаром, схожим на друковану плату, а не проводами.На сучасному ринку упаковка також тепер є окремою частиною процесу, і технологія упаковки також може вплинути на якість і вихід продукту.