Мікроконтроллер Semicon Регулятор напруги IC Chips TPS62420DRCR SON10 Електронні компоненти BOM list service list

Атрибути продукту

| ТИП | ОПИС |

| Категорія | Інтегральні схеми (ІС) Регулятори напруги - DC Імпульсні регулятори постійного струму |

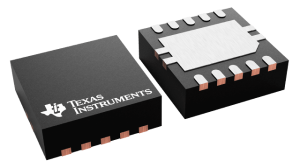

| Виробник | Texas Instruments |

| Серія | - |

| Пакет | Стрічка та котушка (TR) Відрізана стрічка (CT) Digi-Reel® |

| SPQ | 3000T&R |

| Статус продукту | Активний |

| функція | Крок вниз |

| Конфігурація виводу | Позитивний |

| Топологія | Бак |

| Тип виводу | Регульована |

| Кількість виходів | 2 |

| Вхідна напруга (хв.) | 2,5 В |

| Вхідна напруга (макс.) | 6V |

| Вихідна напруга (мін./фікс.) | 0,6 В |

| Вихідна напруга (макс.) | 6V |

| Струм - вихід | 600 мА, 1 А |

| Частота - Перемикання | 2,25 МГц |

| Синхронний випрямляч | Так |

| Робоча температура | -40°C ~ 85°C (TA) |

| Тип монтажу | Поверхневий монтаж |

| Пакет / футляр | 10-VFDFN Відкрита колодка |

| Пакет пристроїв постачальника | 10-VSON (3x3) |

| Базовий номер продукту | TPS62420 |

Концепція упаковки:

Вузький сенс: процес упорядкування, кріплення та з’єднання мікросхем та інших елементів на рамі чи підкладці за допомогою технології плівки та методів мікрофабрикації, що призводить до клем та їх фіксації за допомогою пластичного ізоляційного середовища для формування загальної тривимірної структури.

Загалом кажучи: процес з’єднання та кріплення упаковки до підкладки, збирання її в повну систему або електронний пристрій і забезпечення комплексної роботи всієї системи.

Функції, які досягаються упаковкою мікросхем.

1. передача функцій;2. передача сигналів схеми;3. забезпечення засобів відведення тепла;4. структурний захист і підтримка.

Технічний рівень пакувальної техніки.

Розробка упаковки починається після виготовлення мікросхеми IC і включає всі процеси до того, як мікросхему IC вклеюють і фіксують, з’єднують, герметизують, герметизують і захищають, під’єднують до друкованої плати, а також збирають систему до завершення кінцевого продукту.

Перший рівень: також відомий як упаковка на рівні мікросхеми, — це процес фіксації, з’єднання та захисту мікросхеми IC на пакувальній підкладці або каркасі, що робить її компонентом модуля (складання), який можна легко взяти, транспортувати та з’єднати. на наступний рівень складання.

Рівень 2: процес об’єднання кількох корпусів із рівня 1 з іншими електронними компонентами для формування схемної плати.Рівень 3: процес об’єднання кількох схемних плат, зібраних із пакетів, завершених на рівні 2, для формування компонента або підсистеми на головній платі.

Рівень 4: Процес збирання кількох підсистем у повний електронний продукт.

В чіпі.Процес з’єднання компонентів інтегральної схеми на мікросхемі також відомий як упаковка нульового рівня, тому розробку упаковки також можна розділити на п’ять рівнів.

Класифікація пакетів:

1, відповідно до кількості чіпів IC в пакеті: однокристальний корпус (SCP) і багатокристальний пакет (MCP).

2, відповідно до відмінності ущільнювального матеріалу: полімерні матеріали (пластик) і кераміка.

3, відповідно до режиму з’єднання пристрою та друкованої плати: тип вставки контактів (PTH) і тип поверхневого монтажу (SMT) 4, відповідно до форми розподілу контактів: односторонні контакти, двосторонні контакти, чотиристоронні контакти та нижні шпильки.

Пристрої SMT мають металеві контакти L-типу, J-типу та I-типу.

SIP: однорядна упаковка SQP: мініатюрна упаковка MCP: металева горщикова упаковка DIP: дворядна упаковка CSP: упаковка розміру мікросхеми QFP: чотиристороння плоска упаковка PGA: матрична упаковка BGA: упаковка з масивом кулькової сітки LCCC: безвивідний керамічний носій мікросхем