AM1808EZWT3 Оригінал і новий з конкурентоспроможною ціною в наявності Постачальник мікросхем

Атрибути продукту

| ТИП | ІЛЮСТРУЙТЕ | ВИБЕРІТЬ |

| категорія | Інтегральні схеми (ІС) |

|

| виробник | Texas Instruments |

|

| серії | Sitara™ |

|

| загорнути | лоток |

|

| Статус товару | Активний |

|

| Ядро процесора | ARM926EJ-S |

|

| Кількість ядер/ширина шини | 1 ядро, 32-розрядний |

|

| швидкість | 375 МГц |

|

| Вторинний процесор/DSP | Системний контроль;CP15 |

|

| Контролер оперативної пам'яті | LPDDR、DDR2 |

|

| Прискорення графіки | ні |

|

| Контролери дисплея та інтерфейсу | ЖК |

|

| Ethernet | 10/100 Мбіт/с (1) |

|

| ГОДИНИ | SATA 3 Гбіт/с (1) |

|

| USB | USB 1.1 + PHY (1)、USB 2.0 + PHY (1) |

|

| Напруга - I/O | 1,8 В, 3,3 В |

|

| Робоча температура | 0°C ~ 90°C (TJ) |

|

| Функції безпеки | - |

|

| Тип установки | Тип клею для поверхні |

|

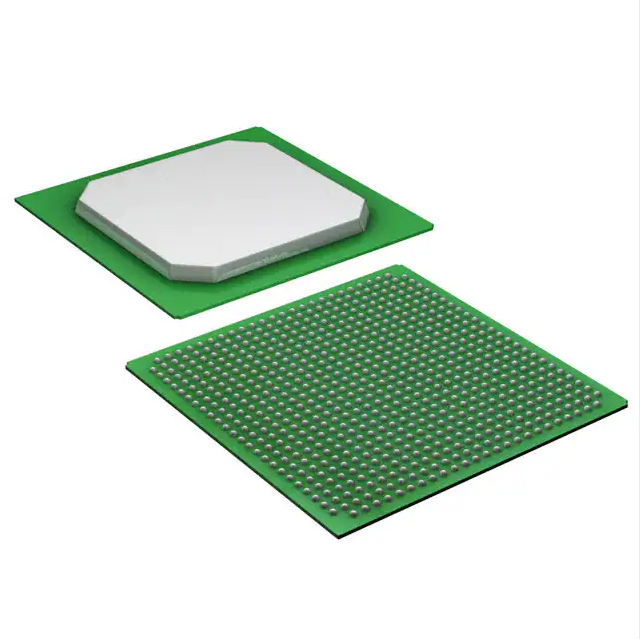

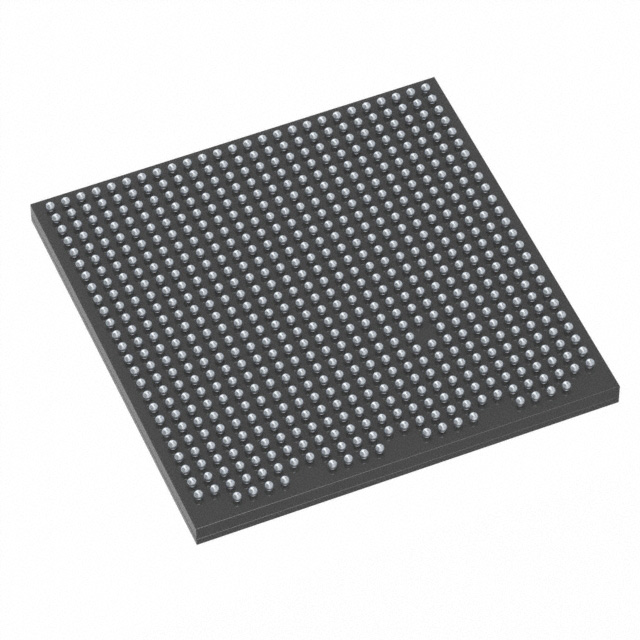

| Пакет/корпус | 361-LFBGA |

|

| Інкапсуляція компонентів постачальника | 361-NFBGA (16x16) |

|

| Додатковий інтерфейс | I²C、McASP、McBSP、SPI、MMC/SD、UART |

|

| Основний номер продукту | AM1808 |

Тип інтегральної схеми

16-розрядний мікропроцесор можна розділити на дві частини, одна частина - це блок виконання (EU), який є частиною, яка виконує інструкції;інша частина - це модуль інтерфейсу шини (BIU), який підключений до шини 8086 і виконує операцію вилучення інструкцій із пам'яті.Після того, як мікропроцесор розділений на EU і BIU, операції отримання інструкцій і виконання інструкцій можуть перекриватися.Частина ЄС має регістровий файл, який складається з 8 16-розрядних регістрів, які можна використовувати для зберігання даних, індексу та покажчика стека, логічного блоку арифметичних операцій (ALU) для виконання арифметичних операцій і логічних операцій, а також регістри прапорів для зберігання умови результатів цих операцій.Ці блоки у виконавчому блоці передають дані через шину даних.Блок інтерфейсу шини також має регістровий файл, де CS, DS, SS і ES є сегментними регістрами для сегментації простору пам'яті.IP є покажчиком інструкції.Внутрішній комунікаційний реєстр також є реєстром для тимчасового зберігання даних.Черга команд призначена для зберігання попередньо отриманого потоку команд.Частина інтерфейсу шини також має суматор адреси, який додає значення регістра сегмента та значення зміщення для отримання 20-бітної фізичної адреси.Дані та адреси підключаються до зовнішньої системної шини 8086 через логіку керування шиною.8086 має 16-розрядну шину даних.Коли процесор і сторонній процесор передають дані, 16-розрядне двійкове число передається в одному класі.8086 має первинну структуру конвеєра, яка може реалізовувати перекриття операцій на чіпі та поза чіпом.