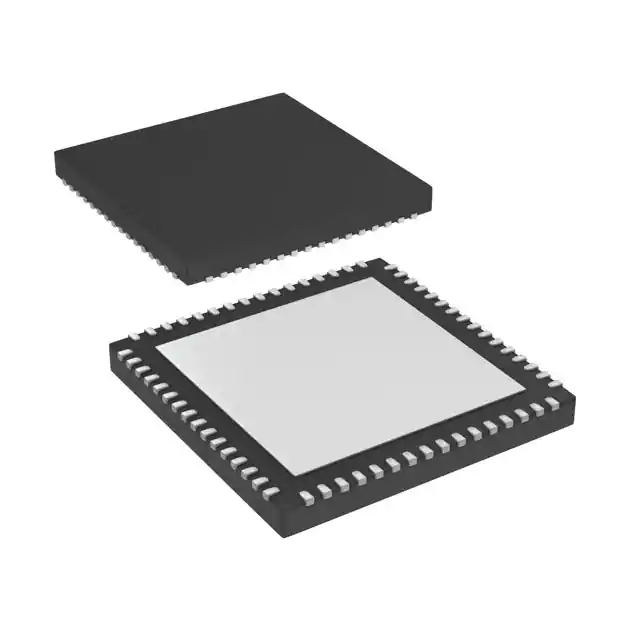

DS90UB936TRGZTQ1 S VQFN-64 UB947Q Мікросхема інтерфейсу

Атрибути продукту

| ТИП | ОПИС |

| Категорія | Інтегральні схеми (ІС) |

| Інтерфейс - серіалізатори, десеріалізатори | |

| Виробник | Texas Instruments |

| Серія | Автомобільний, AEC-Q100 |

| Пакет | Стрічка та котушка (TR) |

| Відрізана стрічка (CT) | |

| Статус частини | Активний |

| функція | Серіалізатор |

| Швидкість передачі даних | 3,36 Гбіт/с |

| Тип введення | LVDS |

| Тип виводу | FPD-Link III, LVDS |

| Кількість входів | 8 |

| Кількість виходів | 2 |

| Напруга - живлення | 1,71 В ~ 1,89 В |

| Робоча температура | нижче нуля 40°C ~ 105°C (TJ) |

| Тип монтажу | Поверхневий монтаж |

| Пакет / футляр | 64-VFQFN Відкрита колодка |

| Пакет пристроїв постачальника | 64-VQFN (9x9) |

| Базовий номер продукту | DS90UB947 |

Тип інтегральної схеми

Перетворення форматів інформації, наприклад послідовне і паралельне перетворення;

Здатність узгоджувати типи та рівні різниці між CPUS та периферійними пристроями в інформації.Наприклад, драйвери горизонтального перетворення, цифро-аналогові або аналого-цифрові перетворювачі тощо;

Примирення часових розбіжностей

Функція декодування та вибору адреси

Налаштуйте логіку керування перериванням і DMA, щоб переконатися, що сигнали переривання та запиту DMA генеруються з дозволом DMA, і що обробка переривання та передача DMA завершуються після прийняття переривання та відповіді DMA.

Інтерфейс вводу/виводу — це електронна схема, як правило, мікросхема чи інтерфейсна плата, що складається зі спеціальних регістрів і відповідних логічних схем керування.Це середовище та міст для обміну інформацією між центральним процесором і пристроями введення/виведення.З’ЄДНАННЯ між центральним процесором і зовнішніми пристроями, пам’яттю та обміном даними має здійснюватися через пристрій інтерфейсу, перший називається інтерфейсом введення/виведення, другий – інтерфейсом пам’яті.Пам'ять, як правило, синхронно керується процесором, схема інтерфейсу відносно проста;Схема інтерфейсу змінюється залежно від типу пристрою введення-виведення, тому інтерфейс умовно називають інтерфейсом введення-виведення.В основному є наступне апаратне забезпечення інтерфейсу вводу/виводу

Існує два методи інтеграції фотонних пристроїв на основі кремнію та CMOS-схем.

Перевага першого полягає в тому, що фотонні пристрої та електронні пристрої можна оптимізувати окремо, але подальше пакування є складним, а комерційне застосування обмежене.Останній складний для проектування та процесу інтеграції двох пристроїв.На даний момент найкращим вибором є гібридна збірка на основі інтеграції ядерних частинок

Наприклад, 1.Мікросхема інтерфейсу введення/виведення

Більшість чіпів є інтегральними схемами, вони вводять різні інструкції та параметри через ЦП і керують відповідною схемою вводу/виводу та простими зовнішніми пристроями для відповідних операцій, чіпи загального інтерфейсу мають синхронізацію/лічильник, контролер переривань, контролер DMA, паралельний інтерфейс тощо на.

Наприклад, 2. Плата керування інтерфейсом вводу/виводу

Залежно від певної логіки, кілька інтегральних схем можуть стати однією частиною, або безпосередньо підключеними до центрального процесора, або плагіни можуть бути вставлені в слоти в системі.

.png)