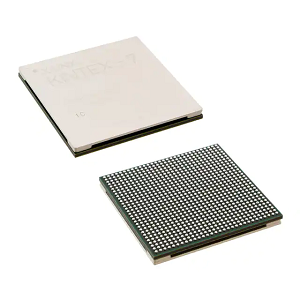

XC7K420T-2FFG901I – вбудовані інтегральні схеми, програмовані вентильні матриці

Атрибути продукту

| ТИП | ІЛЮСТРУЙТЕ |

| категорія | Інтегральні схеми (ІС)Вбудований Програмовані вентильні матриці (FPGA) |

| виробник | AMD |

| серії | Кінтекс®-7 |

| загорнути | лоток |

| Статус товару | Активний |

| DigiKey програмується | Не підтверджено |

| Номер LAB/CLB | 32575 |

| Кількість логічних елементів/блоків | 416960 |

| Загальна кількість біт RAM | 30781440 |

| Кількість входів/виходів | 380 |

| Напруга - джерело живлення | 0,97 В ~ 1,03 В |

| Тип установки | Тип клею для поверхні |

| Робоча температура | -40°C ~ 100°C (ТДж) |

| Пакет/корпус | 900-BBGA、FCBGA |

| Інкапсуляція компонентів постачальника | 901-FCBGA (31x31) |

| Основний номер продукту | XC7K420 |

| ТИП | ІЛЮСТРУЙТЕ |

| категорія | Інтегральні схеми (ІС)Вбудований |

| виробник | AMD |

| серії | Кінтекс®-7 |

| загорнути | лоток |

| Статус товару | Активний |

| DigiKey програмується | Не підтверджено |

| Номер LAB/CLB | 32575 |

| Кількість логічних елементів/блоків | 416960 |

| Загальна кількість біт RAM | 30781440 |

| Кількість входів/виходів | 380 |

| Напруга - джерело живлення | 0,97 В ~ 1,03 В |

| Тип установки | Тип клею для поверхні |

| Робоча температура | -40°C ~ 100°C (ТДж) |

| Пакет/корпус | 900-BBGA、FCBGA |

| Інкапсуляція компонентів постачальника | 901-FCBGA (31x31) |

| Основний номер продукту | XC7K420 |

ПЛІС

Переваги

Переваги FPGA наступні:

(1) FPGA складаються з апаратних ресурсів, таких як логічні комірки, RAM, помножувачі тощо. Раціонально організовуючи ці апаратні ресурси, можна реалізувати апаратні схеми, такі як помножувачі, регістри, генератори адрес тощо.

(2) FPGA можуть бути розроблені за допомогою блок-схем або Verilog HDL, від простих схем затвора до схем FIR або FFT.

(3) FPGA можна нескінченно перепрограмувати, завантажуючи нове проектне рішення всього за кілька сотень мілісекунд, використовуючи реконфігурацію для зменшення витрат на апаратне забезпечення.

(4) Робоча частота ПЛІС визначається мікросхемою ПЛІС, а також конструкцією, і її можна модифікувати або замінити швидшою мікросхемою, щоб відповідати певним вимогам (хоча, звичайно, робоча частота не є необмеженою і може бути збільшеним, але регулюється поточними процесами IC та іншими факторами).

Недоліки

Недоліки FPGA наступні:

(1) FPGA покладаються на апаратну реалізацію для всіх функцій і не можуть реалізувати такі операції, як розгалуження умовних переходів.

(2) FPGA можуть реалізовувати лише операції з фіксованою комою.

Підсумовуючи: FPGA покладаються на апаратне забезпечення для реалізації всіх функцій і їх можна порівняти з виділеними чіпами з точки зору швидкості, але існує великий розрив у гнучкості дизайну порівняно з процесорами загального призначення.

Мови та платформи проектування

Програмовані логічні пристрої є апаратними носіями, які конкретизують встановлені функції та технічні характеристики електронних програм за допомогою технології EDA.ПЛІС, як один із основних пристроїв, які реалізують цей шлях, безпосередньо орієнтовані на користувача, надзвичайно гнучкі та універсальні, прості у використанні та швидко тестуються та впроваджуються в апаратне забезпечення.

Мова опису обладнання (HDL) — це мова, яка використовується для проектування цифрових логічних систем і опису цифрових схем, основними з яких зазвичай використовуються VHDL, Verilog HDL, System Verilog і System C.

Як універсальна мова опису апаратного забезпечення, мова опису апаратного забезпечення дуже високої швидкості інтегрованої схеми (VHDL) має характеристики незалежності від конкретної схеми апаратного забезпечення та незалежності від платформи проектування, з перевагами можливості широкого опису, а не залежить від конкретних пристроїв, а також здатність описувати дизайн складної логіки керування в строгому та короткому коді тощо. Він підтримується багатьма компаніями EDA та широко використовується в галузі електронного проектування.широко використовуваний.

VHDL — це мова високого рівня для проектування схем, і в порівнянні з іншими мовами опису апаратного забезпечення, він має характеристики простої мови, гнучкості та незалежності від конструкції пристрою, що робить його загальною мовою опису апаратного забезпечення для технології EDA та робить технологію EDA більш доступною. доступні для дизайнерів.

Verilog HDL — це широко використовувана мова опису апаратного забезпечення, яку можна використовувати на кількох етапах процесу проектування апаратного забезпечення, включаючи моделювання, синтез і імітацію.

Переваги Verilog HDL: схожий на C, простий у вивченні та гнучкий.Чутливий до регістру.Переваги в написанні стимулу та моделювання.Недоліки: багато помилок неможливо виявити під час компіляції.

Плюси VHDL: строгий синтаксис, чітка ієрархія.Недоліки: тривалий час ознайомлення, недостатньо гнучкий.

Програмне забезпечення Quartus_II — це повне мультиплатформене середовище проектування, розроблене компанією Altera, яке може задовольнити потреби в проектуванні різних ПЛІС і CPLD, а також є комплексним середовищем для проектування програмованих систем на кристалі.

Vivado Design Suite, інтегроване середовище проектування, випущене постачальником FPGA Xilinx у 2012 році. Воно включає високоінтегроване середовище проектування та нове покоління інструментів від рівня системи до рівня IC, усі побудовані на спільній масштабованій моделі даних і спільному середовищі налагодження.Xilinx Vivado Design Suite надає IP-ядра FIFO, які можна легко застосувати до проектів.